1. Интеграль схемалар турында

1.1 Интеграль схемаларның төшенчәсе һәм тууы

Интеграль схема (IC): транзистор һәм диод кебек актив җайланмаларны резисторлар һәм конденсаторлар кебек пассив компонентлар белән берләштерә торган җайланма, билгеле бер эшкәртү техникасы сериясе аша.

Ярымүткәргечкә (интеграцияләнгән) схема яки система (кремний яки галлий арсенид кебек кушылмалар кебек) вафер билгеле бер челтәр бәйләнеше буенча, аннары билгеле функцияләрне башкару өчен кабыкка төрелгән.

1958-нче елда Техас Инструменты (TI) электрон җиһазларын миниатюризацияләү өчен җаваплы Джек Килби интеграль схемалар идеясын тәкъдим итте:

"Конденсаторлар, резисторлар, транзисторлар һ.б. кебек барлык компонентлар бер материалдан ясалырга мөмкин булганлыктан, мин аларны ярымүткәргеч материал кисәгендә ясап, аннары үзара тоташтырып, тулы схема булдырырга мөмкин дип уйладым."

1958 елның 12 сентябрендә һәм 19 сентябрендә Килби интеграль схеманың тууын искә алып, фаза-смена осиллаторын һәм триггерын җитештерүне һәм күрсәтүне тәмамлады.

2000-нче елда Килби физика буенча Нобель премиясенә лаек булды. Нобель премиясе комитеты бервакыт Килби "заманча мәгълүмат технологияләренә нигез салды" дип аңлатма бирде.

Түбәндәге рәсемдә Килби һәм аның интеграль схема патенты күрсәтелгән:

1.2 Ярымүткәргеч җитештерү технологиясен үстерү

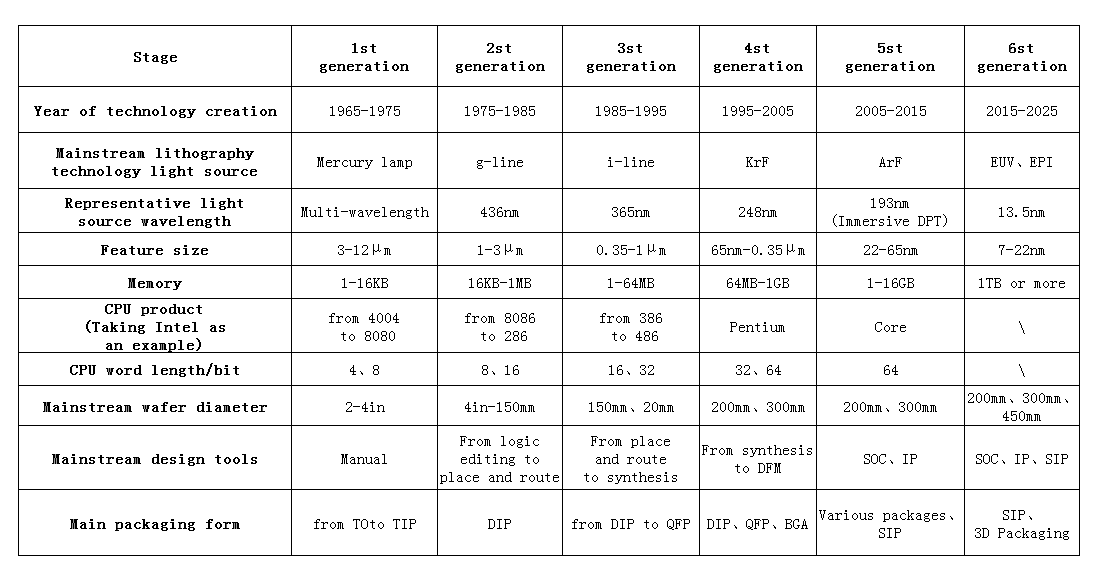

Түбәндәге рәсем ярымүткәргеч җитештерү технологиясенең үсеш этапларын күрсәтә:

1.3 Интеграль схема индустриясе чылбыры

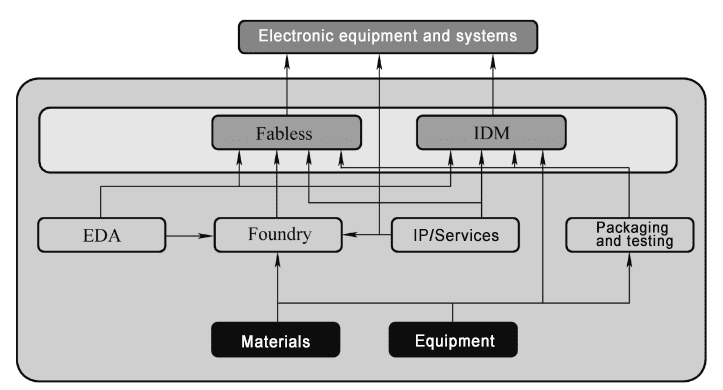

Ярымүткәргеч индустрия чылбырының составы (нигездә интеграль схемалар, шул исәптән дискрет җайланмалар) югарыдагы рәсемдә күрсәтелгән:

- Fabless: Производство линиясе булмаган продуктларны проектлаучы компания.

- IDM: Интеграль җайланма җитештерүче, интеграль җайланма җитештерүче;

- IP: Схема модулын җитештерүче;

- EDA: Электрон Дизайн Автоматик, электрон дизайн автоматизациясе, компания нигездә дизайн кораллары белән тәэмин итә;

- Фабрика; Чип җитештерү хезмәтләрен күрсәтүче вафин фабрикасы;

- Пакетлау һәм сынау компанияләре: нигездә Fabless һәм IDM хезмәт күрсәтү;

- Материаллар һәм махсус җиһаз компанияләре: нигездә чип җитештерү компанияләре өчен кирәкле материаллар һәм җиһазлар белән тәэмин итәләр.

Ярымүткәргеч технологиясе ярдәмендә җитештерелгән төп продуктлар интеграль схемалар һәм дискрет ярымүткәргеч җайланмалар.

Интеграль схемаларның төп продуктлары:

- Стандарт өлешләрне куллану (ASSP);

- Микропроцессор берәмлеге (MPU);

- Хәтер

- Заявка конкрет интеграль схема (ASIC);

- Аналог схемасы;

- Гомуми логик схема (Логик схема).

Ярымүткәргеч дискрет җайланмаларның төп продуктлары:

- Диод;

- Транзистор;

- Электр җайланмасы;

- Volгары көчәнешле җайланма;

- Микродулкынлы җайланма;

- Оптоэлектроника;

- Сенсор җайланмасы (сенсор).

2. Интеграль схема җитештерү процессы

2.1 Чип җитештерү

Кремний вафатында берьюлы дистәләгән, хәтта дистәләгән мең махсус чип ясарга мөмкин. Кремний вафатындагы фишкалар саны продукт төренә һәм һәр чипның зурлыгына бәйле.

Кремний вафиннары гадәттә субстратлар дип атала. Кремний вафатларның диаметры еллар дәвамында арта бара, башында 1 дюймнан да азрак кулланыла торган 12 дюймга (якынча 300 мм), һәм 14 дюйм яки 15 дюймга күчә.

Чип җитештерү гадәттә биш этапка бүленә: кремний вафер әзерләү, кремний вафин җитештерү, чип сынау / җыю, җыю һәм төрү, һәм соңгы сынау.

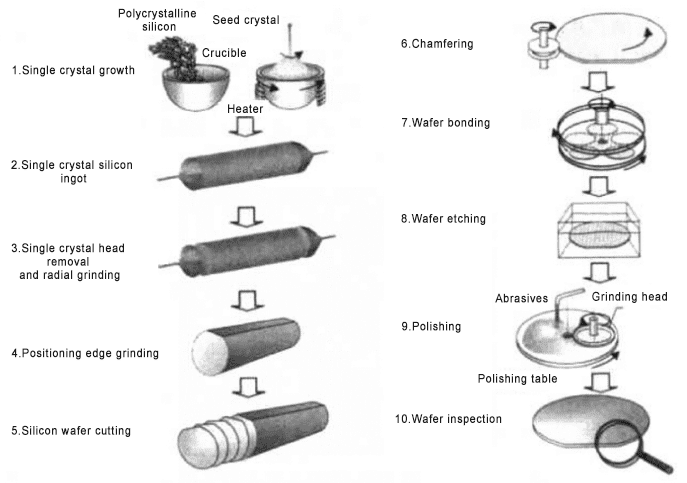

(1)

Кремний вафины әзерләү:

Чимал ясау өчен кремний комнан чыгарыла һәм чистартыла. Махсус процесс тиешле диаметрлы кремний инготлар җитештерә. Аннары микрочип ясау өчен нечкә кремний вафаларга кисәләр.

Ваферлар конкрет спецификацияләргә әзер, мәсәлән, теркәлү кыры таләпләре һәм пычрану дәрәҗәсе.

(2)Кремний вафин җитештерү:

Чип җитештерү дип тә атала, ялан кремний вафин кремний вафин җитештерү заводына килеп җитә, аннары төрле чистарту, кино формалаштыру, фотолитография, эфинг һәм допинг адымнары аша уза. Эшкәртелгән кремний вафин кремний вафатында даими урнаштырылган интеграль схемаларның тулы җыелмасына ия.

(3)Кремний ваферларын сынау һәм сайлау:

Кремний вафин җитештерү тәмамланганнан соң, кремний вафлары сынау / сорт өлкәсенә җибәрелә, анда аерым чиплар тикшерелә һәм электр белән сынала. Кабул ителә торган һәм кабул ителмәгән чиплар соңыннан тәртипкә китерелә, җитешсез фишкалар билгеләнә.

(4)Монтажлау һәм төрү:

Ваферны сынау / сортлаудан соң, ваферлар монтажлау һәм төрү адымына керәләр, аерым чипларны саклагыч труба пакетына урнаштыру өчен. Ваферның арткы ягы субстрат калынлыгын киметү өчен җир.

Wafәр вафинның артына калын пластик пленка беркетелә, аннары бриллианттан ясалган пычак кулланыла, алгы ягында язучы сызыклары буенча һәр вафиндагы чипларны аеру өчен.

Кремний вафаты артындагы пластик пленка кремний чипны егылудан саклый. Монтажлау заводында яхшы чиплар басыла яки эвакуацияләнә, монтаж пакеты. Соңрак, чип пластик яки керамик кабыкка мөһерләнгән.

(5)Соңгы тест:

Чипның функциональлеген тәэмин итү өчен, һәр пакетланган интеграль схема җитештерүченең электр һәм экологик характеристик параметр таләпләрен канәгатьләндерү өчен сынала. Соңгы сынаудан соң, чип клиентка махсус урында җыю өчен җибәрелә.

2.2 Процесс бүлеге

Интеграль схема җитештерү процесслары гадәттә түбәндәгеләргә бүленә:

Фронт: Алгы процесс, гадәттә, транзистор кебек җайланмалар җитештерү процессына карый, нигездә изоляция, капка структурасы, чыганак һәм дренаж, контакт тишекләре һ.б.

Арткы.

Урта этап: Транзисторларның эшләвен яхшырту өчен, 45нм / 28нмнан соң алдынгы технология төеннәре югары к каплы диэлектрик һәм металл капка процессларын кулланалар, һәм транзистор чыганагы һәм дренаж структурасы әзерләнгәннән соң капка процессларын һәм җирле үзара бәйләнеш процессларын өстәргә. Бу процесслар алгы-процесс белән арткы процесс арасында, һәм традицион процессларда кулланылмый, шуңа күрә алар урта этап процесслары дип атала.

Гадәттә, контакт тишеген әзерләү процессы - алгы процесс белән арткы процессны бүлүче сызык.

Контакт тишеге: беренче катлы металл үзара бәйләнеш сызыгын һәм субстрат җайланмасын тоташтыру өчен кремний вафатында вертикаль рәвештә тишелгән тишек. Вольфрам кебек металл белән тутырылган һәм җайланма электродын металл үзара бәйләнеш катламына алып бару өчен кулланыла.

Чокыр аша: Бу ике металл катлам арасындагы диэлектрик катламда урнашкан һәм гадәттә бакыр кебек металл белән тутырылган металл үзара бәйләнеш сызыкларының ике янәшә катламы арасында тоташу юлы.

Киң мәгънәдә:

Алгы процесс: Киң мәгънәдә, интеграль схема җитештерү шулай ук сынау, төрү һәм башка адымнарны кертергә тиеш. Тест һәм төрү белән чагыштырганда, компонент һәм үзара бәйләнеш җитештерү - интеграль схема җитештерүнең беренче өлеше, бергәләп фронтовик процесслар дип атала;

Арткы процесс: Тест һәм пакетлау арткы процесс дип атала.

3. Кушымта

SMIF : Стандарт механик интерфейс

AMHS Material Автоматлаштырылган материал тапшыру системасы

OHT head Өстән күтәрү

FOUP : Фронтны ачу Бердәм Под 12 12 дюйм (300 мм) ваферга кадәр

Иң мөһиме,Семицера тәэмин итә алаграфит өлешләре, йомшак / каты тойгы,кремний карбид өлешләре, CVD кремний карбид өлешләре, һәмSiC / TaC капланган өлешләр30 көн эчендә тулы ярымүткәргеч процессы белән.Без Кытайда озак вакытлы партнер булырга түземсезлек белән көтәбез.

Пост вакыты: 15-2024 август